# COMPARATIVE STUDY ON THE ELECTRICAL CHARACTERISTICS OF Au/n-Si AND Au/P3HT/n-Si DIODES

# A.ASIMOV<sup>a</sup>, A. KIRSOY<sup>b</sup>

<sup>a</sup>Institute of Physics, Academy of Sciences of Azerbaijan, 33 H. Javid, Baku Azerbaijan–1143 <sup>b</sup>Department of Physics, Faculty of Sciences and Arts, Uludag University, 16059 Gorukle, Bursa, Turkey

Corresponding author: E-mail address: fizikasimov@gmail.com Tel: 518991515

In this work, we have fabricated Au/P3HT/n-Si and Au/n-Si Schottky barrier diodes (SBDs) to investigate the effect of polymer interfacial layer on the electronic parameters. Electronic parameters of these two diodes were calculated from the currente-voltage characteristics. It was seen that the ideality factor value of 3.47 eV calculated for the Au/P3HT/n-Si device was higher than the value of 1.18 eV of the Au/n-Si Schottky diodes. The  $R_s$  values obtained from Cheung's function are 18.6 and 495 for Au/n-Si and Au/P3HT/n-Si, respectively.

**Keywords:** Metal semiconductor-structure, conductive polymer, P3HT, ideality factor **PACS:** 6855 jk

#### 1. INTRODUCTION

Conductive polymeric materials have advantages such as, a good mechanical flexibility, high hole mobility, stable in the atmosphere and easy fabrication [3–5]. There has been much interest in the conductive polymeric materials in the study area of solar cells, light emitting diodes and thin film transistors. Among the conducting polymers, P3HT has specific properties such as a good mechanical flexibility, high hole mobility and is stable in the atmosphere. The electronic parameters of the diodes such as the ideality factor, the barrier height, the interface state density, the thickness of the interfacial layer and series resistance (R<sub>s</sub>) from current-voltage (I-V) and capacitance-voltage (C-V) measurements [6-10]. In this will fabricate the Au/P3HT/n-Si metal/polymer/semiconductor (MPS) device by spin coating method.

## 2. EXPERIMENTAL PROCEDURES

n-Type Si semiconductor wafer with (100) orientation and 280 mm thickness was used before making contacts, the wafer was chemically cleaned using the RCA cleaning procedure (i.e.10 min boil in  $H_2SO_4 + H_2O_2$  followed by a 10 min  $HCl + H_2O_2 + 6H_2O$ at 60  $^{0}$ C). The ohmic contact with a thickness of ~1500 Å was made by evaporating 99.9% purity Au metal on the back surface of the n-Si substrate, then was annealed at 550 °C for 3 min in N<sub>2</sub> atmosphere. Front surface of samples were coated with a conducting polymer poly(3-hexylthiophene) (P3HT) (fig.1) film by spin coating (VTC-100) with 1200 rpm for 60 s. After that rectifier Schottky contacts were formed on the other faces by evaporating ~2000Å thick Au. The I–V measurements were performed using a Keithley 6517A electrometer and C-V measurements were carried out at room temperature with a Keithley HP-4194 C-V Analyzer.

# 3. ANALYSÍS OF Au/P3HT/n-Si JUNCTÍON DÍODE AT ROOM TEMPERATURE

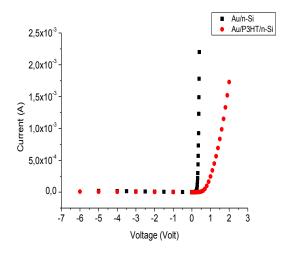

The forward-and reverse-bias I-V characteristics of

the Au/P3HT/n-Si contact and are ference Au/n-Si diode at room temperature are shown in fig. 1. As clearly seen from fig. 1, the Au/P3HT/n-Si structure exhibits a good rectifying behavior. We analyze the experimental I–V characteristics by the forward bias thermionic emission (TE) theory given as follows [1-2]

$$I = I_0 \exp\left(\frac{q(V - IR)}{nkT}\right) \left[1 - \exp\left(\frac{-q(V - IR)}{kT}\right)\right]$$

(1)

where

$$I_0 = AA^*T^2 \exp\left(-\frac{q\phi_{b0}}{kT}\right) \tag{2}$$

is the saturation current,  $\Phi_{b0}$  (I-V) is the zero bias barrier height, A\* is the Richardson constantant and equals to 120 Acm<sup>-2</sup>K<sup>-2</sup> for n-type Si, where q is the electron charge, n is the ideality factor. From eq.(1), ideality factor n can be written as

$$n = \frac{q}{kT} \left( \frac{dV}{d(\ln I)} \right) \tag{3}$$

n equals to one for an ideal diode. However, n has usually a value greater than unity. High values of n can be attributed to the presence of the interfacial thin native oxide layer and a wide distribution of low-SBH patches (or barrier height inhomogeneities), and, therefore, to the bias voltage dependence of the SBH [1-2]. Fig.1 presents the forward bias current–voltage (I–V) characteristics of the Au/P3HT/n-Si/Au structure. The  $\Phi_{b0}$  and n values of these diodes were calculated from a linear fit of the lnI vs V plots in fig. 1 by using the eqs. (2) and (3) and the obtained values are 0.78 eV and 1.18 for Au/n-Si/Au diode, 0.75 eV and 3,47 for Au/P3HT/n-Si/Au diode, respectively. It has been observed that ideality factor of Au/P3HT/n-Si structure increases about 2.29 with respect to Au/n-Si at room temperature.

Fig 1. The forward and reverse bias semi-logarithmic I–V characteristics of Au/n-Si and Au/P3HT/n-Si Schottky barrier diodes at room temperature.

The value of the ideality factor is greater than unity. The high values in the ideality factor are caused possibly by various effects such as inhomogeneities of P3HT film thickness, non-uniformity of the interfacial charges and series resistance, [11-14].

The values of the series resistance is determined from following functions using eq. (4).

$$\frac{dV}{d(\ln I)} = IR_s + n\left(\frac{kT}{q}\right) \tag{5}$$

$$H(I) = V - n \left(\frac{kT}{q}\right) \ln \left(\frac{I_0}{AA * T^2}\right) \tag{6}$$

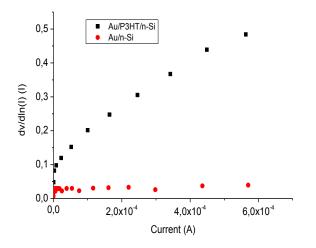

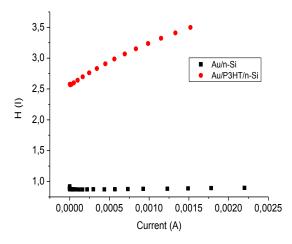

In fig. 2 (a) and (b), the values of  $dV/d(\ln I)$ —I and H(I)—I are plotted for Au/P3HT/n-Si and Au/n-Si Schottky contacts , respectively. A plot of  $dV/d\ln(I)$  vs I

will gives  $R_s$  as the slope and n the y-axis intercept [15]. The values of n and Rs for SBD were derived from fig. 2 by using eqs. (5) and (6), respectively, and they were presented in Table 1. The  $R_s$  values obtained from eq. (5) are 18.6 and 495 for Au/n-Si and Au/P3HT/n-Si, respectively. The high series resistance  $R_s$  value can be attributed to the presence of a native interfacial layer between metal and semiconductor. The interface states and interfacial layer between the metal/semiconductor structures play an important role in the determination of the electronic parameters of the diodes. Density of interface states proposed by Card and Rhoderick can be simplified and given as [13;14]:

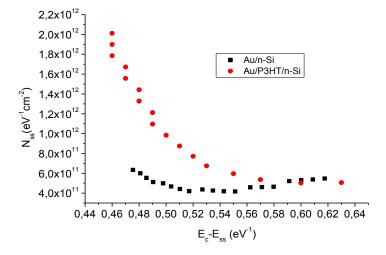

$$N_{ss}(V) = \frac{1}{q} \left\{ \frac{\varepsilon_i}{\delta} \left[ n(V) - 1 \right] - \frac{\varepsilon_s}{W_D} \right\} \tag{7}$$

where  $N_{ss}$  is the density of the interface states,  $\delta$  is the thickness of interfacial layer,  $W_d$  is the space charge width, and n(V) is the voltage-dependent ideality factor,  $\varepsilon_s=11.8\varepsilon_0$  and  $\varepsilon_i=3\varepsilon_0$  are the permittivity of the semiconductor and conducting polymer (P3HT), respectively. In n-type semiconductors, the energy of the interface states  $E_{ss}$  with respect to the bottom of the conduction band at the surface of the semiconductor is given by

$$E_c - E_{ss} = q(\Phi_e - V_D) \tag{8}$$

Where  $V_D$  is the applied voltage drop across the depletion layer and  $\Phi_e$  is the effective barrier height.  $N_{ss}$  values are obtained via eq.(11). Fig. 3 shows the energy distribution profiles of  $N_{ss}$  extracted from the forward bias I–V characteristics for Au/P3HT/n-Si and Au/n-Si Schottky barrier diodes . The magnitude of  $N_{ss}$  ranges from  $5.05 \times 10^{11}$  at Ec—0.63 eV to  $2.01 \times 10^{12}$  eV<sup>-1</sup> cm<sup>-2</sup> at Ec—0.46 eV for Au/P3HT/n-Si SBD and  $5.46 \times 10^{11}$  at Ec—0.61 eV to  $6.33 \times 10^{11}$  eV<sup>-1</sup> cm<sup>-2</sup> at Ec—0.47 eV for Au/n-Si Schottky barrier diodes.

Fig 2. The plots of dV/d ln I and H(I) vs. current of Au/n-Si and Au/P3HT/n-Si Schottky barrier diodes at room temperature.

#### COMPARATIVE STUDY ON THE ELECTRICAL CHARACTERISTICS OF Au/n-Si AND Au/P3HT/n-Si DIODES

Table 1.

The experimental values of some parameters obtained from the forward bias I–V characteristics of Au/n-Si and Au/P3HT/n-Si Schottky barrier diodes at room temperature.

| Diodes       | n    | $\Phi_{\rm b}$ | $I_{o}$ | dV/dLn(I) |             | H(I)        |            | N <sub>ss</sub>      |

|--------------|------|----------------|---------|-----------|-------------|-------------|------------|----------------------|

|              |      |                |         | N         | $R_{\rm s}$ | $R_{\rm s}$ | $\Phi_{b}$ |                      |

| Au/n-Si      | 1,18 | 0,78           | 7,56e-9 | 1,12      | 18,6        | 13,5        | 0,73       | 6,3x10 <sup>11</sup> |

| Au/P3HT/n-Si | 3,47 | 0,75           | 2,08E-8 | 6,07      | 495         | 611         | 0,74       | 2,1x10 <sup>12</sup> |

Fig. 3. The energy distribution profiles of  $N_{ss}$  for Au/n-Si and Au/P3HT/n-Si Schottky barrier diodes at room temperature.

### IV. CONCLUSION

Electronic properties of the Au/n-Si and Au/P3HT/n-Si Schottky barrier diode have been investigated by means of I–V measurements at room temperature. It was seen that the ideality factor value of

3.47 eV calculated for the Au/P3HT/n-Si device was higher than the value of 1.18 eV of the Au/n-Si Schottky barrier diodes. The values of the ideality factor, series resistance and barrier height obtained from Cheung and Norde method were compared, and it was seen that there was an agreement with each other.

- [1] S.M. Sze. Physics of Semiconductor Devices, 2nd ed., John Wiley & Sons, New York, 1981.

- [2] E.H. Rhoderick, R.H. Williams. Metal— Semiconductor Contacts, Clerendon, Oxford, 1988.

- [3] T. Tunç, İ. Uslu, İ. Dökme, Ş. Altındal, H. Uslu. International Journal of Polymeric Materials (2010)

- [4] F. Yakuphanoglu. Synthetic Metals 160 (2010) 1551–1555.

- [5] P. Anuragudom, J. El-daye, P. Chinwangso, R.C. Advincula, S. Phanichphant, T.R. Lee. Polymer International 60 (2011) 660–665.

- [6] Ahmed Fatime E, Yassin OA. Microelectron J 2007; 38:834.

- [7] F. Yakuphanoglu. J. Alloys Compd. 494 (2010) 451e455.

- [8] Nguyen N.C, Potje-Kamloth K. Thin Solid Films 1999;338:142.

- [9] W. Brütting. Physics of Organic Semiconductors, Wiley-VCH-Verlag GmbH & Co.KGaA, Weinheim, 2005.

- [10] E.J. Meijer, A.V.G. Mangnus, C.M. Hart, D.M. de Leeuw, T.M. Klapwijk. Appl. Phys. Lett. 78, (2001).

- [11] F. Yakuphanoğlu, M. Shah and W. Aslam Farooq. A. Phys. Polonica A 120 (2011) 3

- [12] E. Voroshazi, B.Verreet, T.Aernouts, P.Heremans. Solar Energy Mater. Solar Cells 95 (2011) 1303–1307.

- [13] Norde H. J. Appl. Phys. 1979;50:5052.

- [14] *H.C. Card, E.H. Rhoderick.* J. Phys. D: Appl. Phys. 4 (1971) 1589.

Recevied: 26.04.2016